本文共 859 字,大约阅读时间需要 2 分钟。

//

自定义ip:

(1),在settings里面设置ip 打包属性

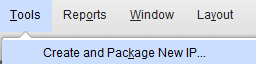

(2),在tools点封装向导,

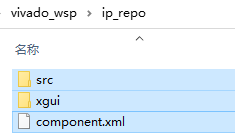

最后生成的文件如下图只有其中3个是有用的(src/xgui/component.xml [其中component.xml用vivado打开后是可以修改ip里面参数的]),放到一个新的文件夹share给使用者即可,使用者只要在settings中添加ip目录即可

自定义ip的有点提供了他人使用时的gui用户向导(并且保留了parameter参数),但源码不能加密(src文件夹被一览无余),意义不大,和直接share源码给别人没有区别。

使用edif/dcp:

使用edif虽然别人看不到源码,但是却也失去了parameter的定制性。不过某些parameter可以使用寄存器替换。

(1)选中需要的模块设为顶层

在综合设置窗口的Options下面最后一项More Options一栏写入-no_iobuf;

![]()

disable掉xdc相关文件,因为我们要封装的verilog代码是纯verilog

(2)完成综合过程并打开综合结果,在tcl_console中输入:

write_edif *.edf

write_verilog -mode synth_stub *.v

使用网表文件还有问题,就是edf文件不能做行为仿真,需要综合后才可以仿真,这大大降低了仿真的效率!

尝试使用vivado的edf转v功能:

打开新的vivado窗口或制作成tcl脚本

read_edif *.edf

link_design -name netlist1 -top * -part *

write_verilog -mode funcsim *.v

将生成的.v用于仿真是ok的,但是这个.v只能仿真,生成bit还得用上一步的edf!

使用时把edf及其转化的.v文件都包含进来并设置好对应的used in 属性即可,仿真和综合都会调用对应的文件而不会混淆!

如果使用dcp的方式据说可以封装带有ip核的源码,具体看下面文章:

参考:

转载地址:http://ydyws.baihongyu.com/